1994年に ISO/IEC 10918-1が規格化されて以来、現在でも静止画の保存フォーマットとしてJPEGが使われ続けております。

そこでTMCでは、ISO/IEC 10918-1の標準化規格に準拠したベースライン方式のJPEGハードウェアIPを、非常にコンパクトかつ高速な圧縮IPとして開発し製品化しました。

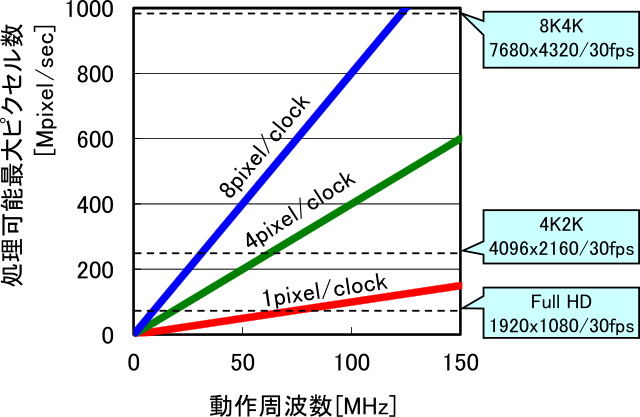

JPEG エンコーダ/デコーダ 1pixel/clock

| 圧縮フォーマット | JPEG (ISO/IEC 10918-1) |

| スループット | 1pixel/clock @ YCbCr 4:2:2 |

| 画像サイズ | 65K × 65K pixel(最大) |

| 画像フォーマット | YCbCr 4:4:4/4:2:2/4:2:0/4:0:0 |

| 画像ビット深度 | 8bit |

| インターフェース仕様 | AXI3 |

このIPはYCbCr・YUVに対応 しています

パンフレットはこちら

JPEG エンコーダ/デコーダ 4pixel/clock

| 圧縮フォーマット | JPEG (ISO/IEC 10918-1) |

| スループット | 4pixel/clock @ YCbCr 4:2:2 |

| 画像サイズ | 65K × 65K pixel(最大) |

| 画像フォーマット | YCbCr 4:4:4/4:2:2/4:2:0/4:0:0 |

| 画像ビット深度 | 8bit |

| インターフェース仕様 | AXI3 |

このIPはYCbCr・YUVに対応 しています

パンフレットはこちら

JPEG エンコーダ 8pixel/clock

| 圧縮フォーマット | JPEG (ISO/IEC 10918-1) |

| スループット | 8pixel/clock @ YCbCr 4:2:2 |

| 画像サイズ | 65K × 65K pixel(最大) |

| 画像フォーマット | YCbCr 4:4:4/4:2:2/4:2:0/4:0:0 |

| 画像ビット深度 | 8bit |

| インターフェース仕様 | AXI3 |

このIPはYCbCr・YUVに対応 しています

パンフレットはこちら